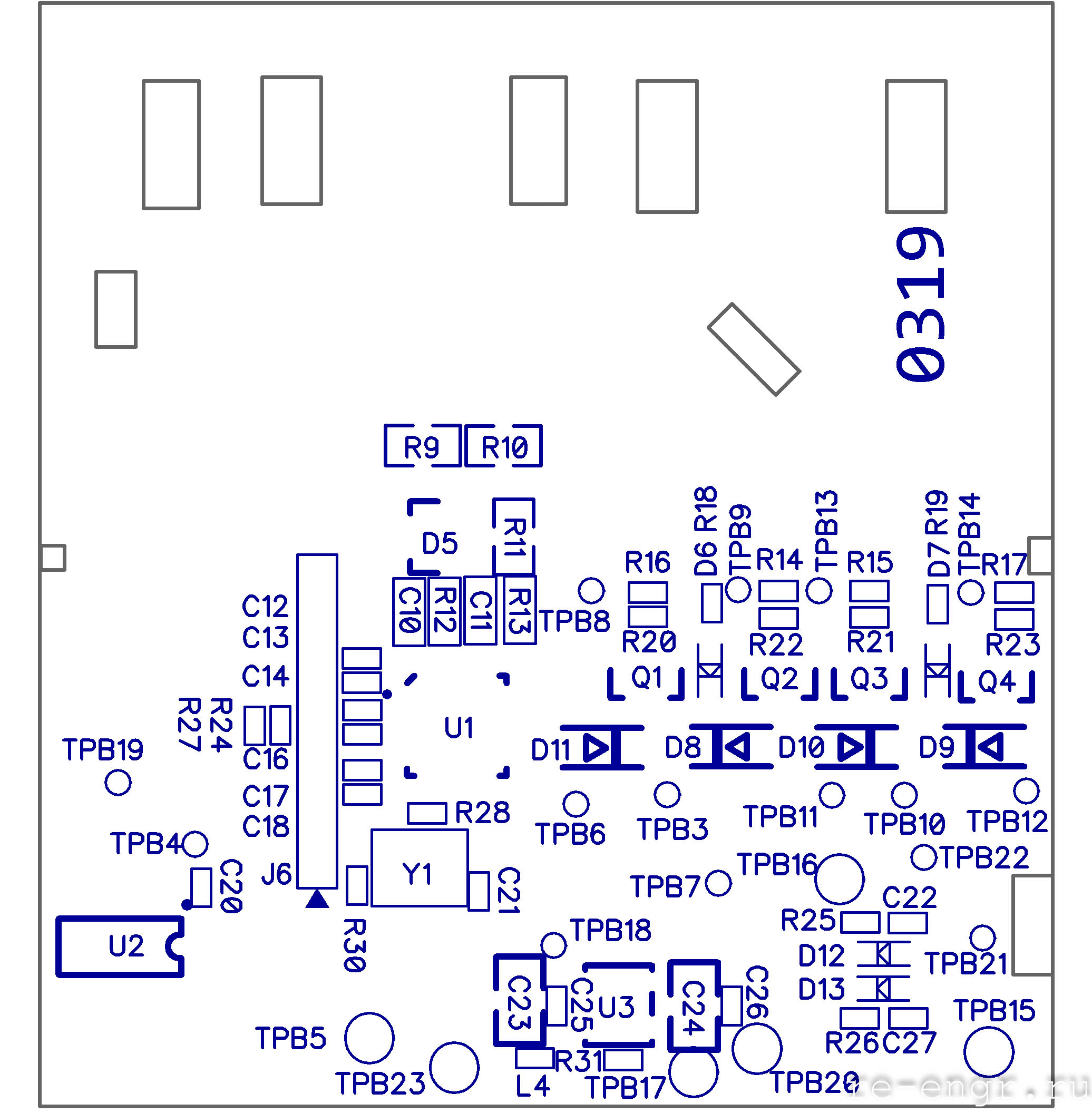

Aqara relay (LLKZMK11LM). Схема платы с реле.

Продолжение исследования устройства Aqara реле…

Продолжение исследования устройства Aqara реле…

План работ остается прежним:

- Восстановление схемы платы с контроллером;

- Восстановление схемы платы с реле;

- Исследование девайса со стороны zigbee (ep, кластера и т.п.);

- Извлечение прошивки из JN5169;

- Исследование измерительной микросхемы PL7211;

Новые возможности

Восстанавливая схему, обнаружил несколько интересных особенностей устройства о которых ранее не знал:

-

Широкий диапазон питающего напряжение (от 15 вольт). Я провел эксперименты с источником питания 24В постоянного тока. N - плюс, L - общий. Устройство уверенно запускается. Вторичные напряжения составляют 5.2В и 3.3В.

В момент переключения реле (для поляризованного реле это единственный момент для потребления тока) нет провала вторичных напряжений.

Надо еще провести климатические испытания, особенно при минусовой температуре. Сфера применения этого устройства, в оригинальном виде, расширяется. Вот только напряжение и ток измеряются некорректно. -

Входы для кнопок S1 и S2 не имеют аппаратной ‘заточки’ быть только входами. В альтернативной прошивке их можно использовать как дискретные выходы, PWM, а при небольшой аппаратной доработке — как ЦАП.

-

JN5169 можно прошить через разъем J6 на плате с реле. Это удобнее чем через разъем JP2 на плате процессора. К тому же на J6 выведены сигналы для взаимодействия с PL7211.

-

PL7211 имеет ряд незадействованных GPIO. Я еще не вникал в особенности работы с этой микросхемой, но вероятно этими GPIO можно рулить из JN5169. Это так же расширяет функционал для альтернативной прошивки.

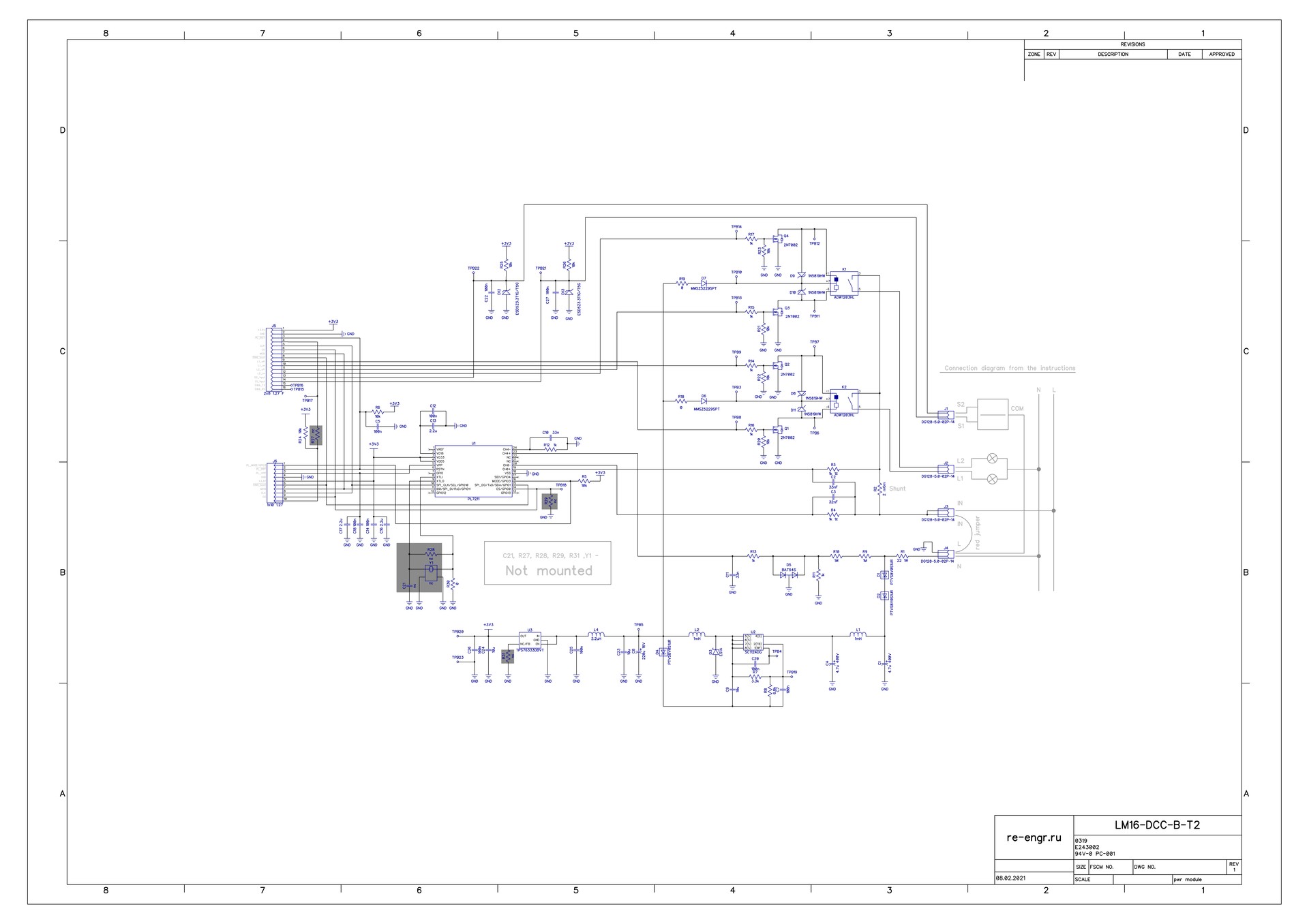

Так же на схеме видно как организована измерительная часть тока/напряжения и для чего нужна красная перемычка.

Некоторые элементы на схеме имеют серый фон. Это значит что они небыли смонтированы на плате. Возможно тип этих компонентов опознан некорректно.

Интересна надпись Frank&Will на слое Top. Похоже на пасхалку. Возможно это как-то связано с этим человеком.

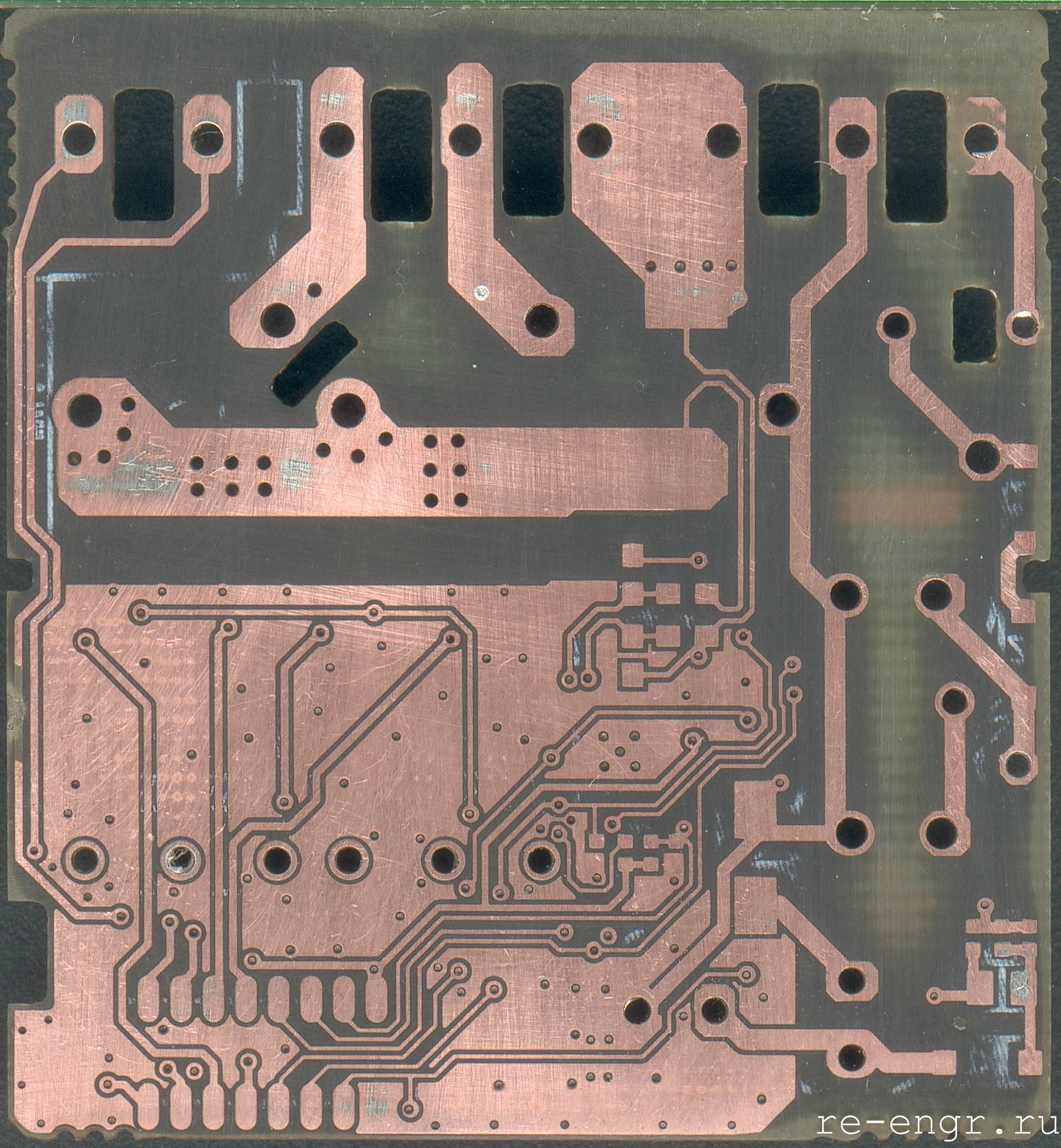

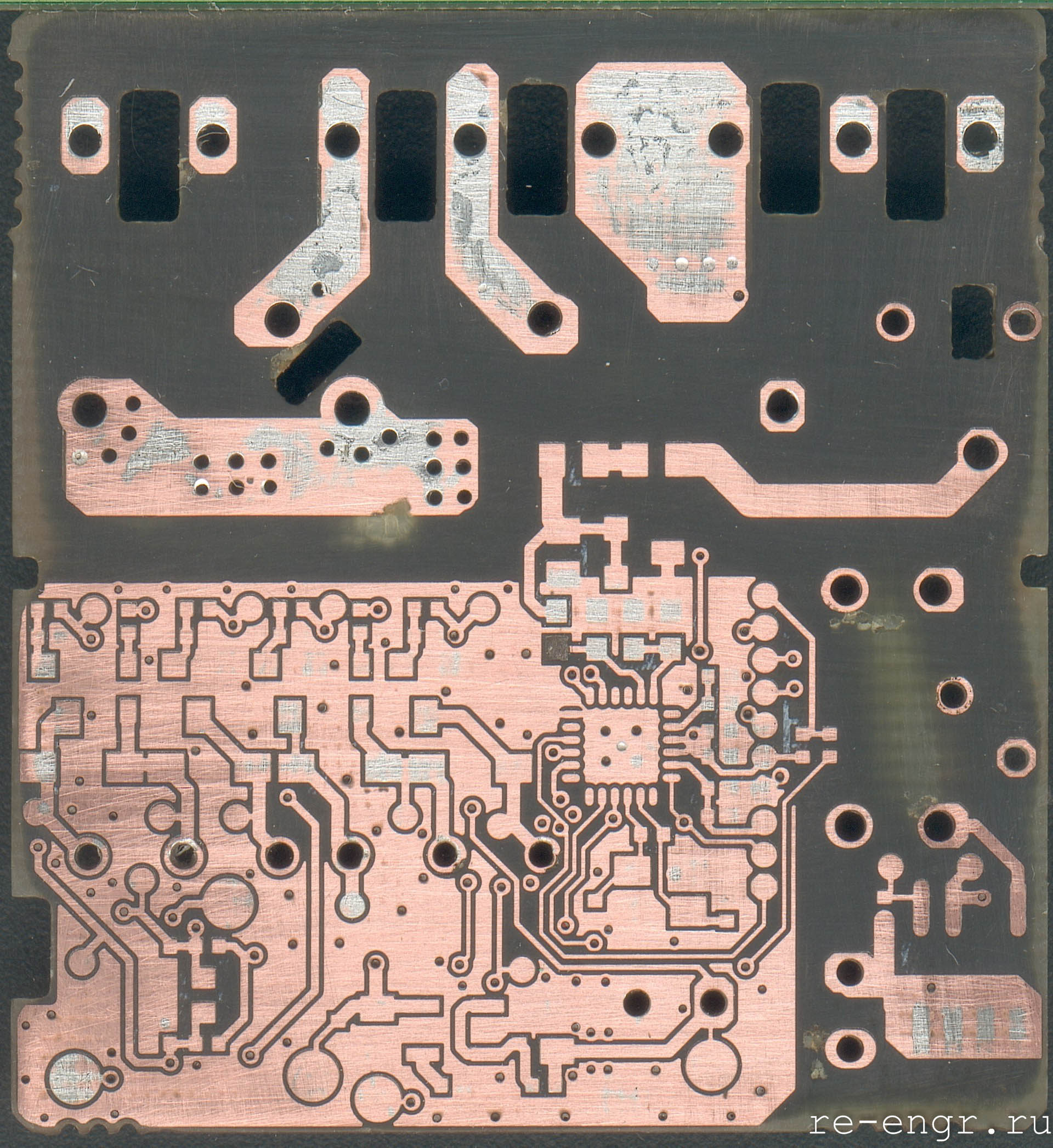

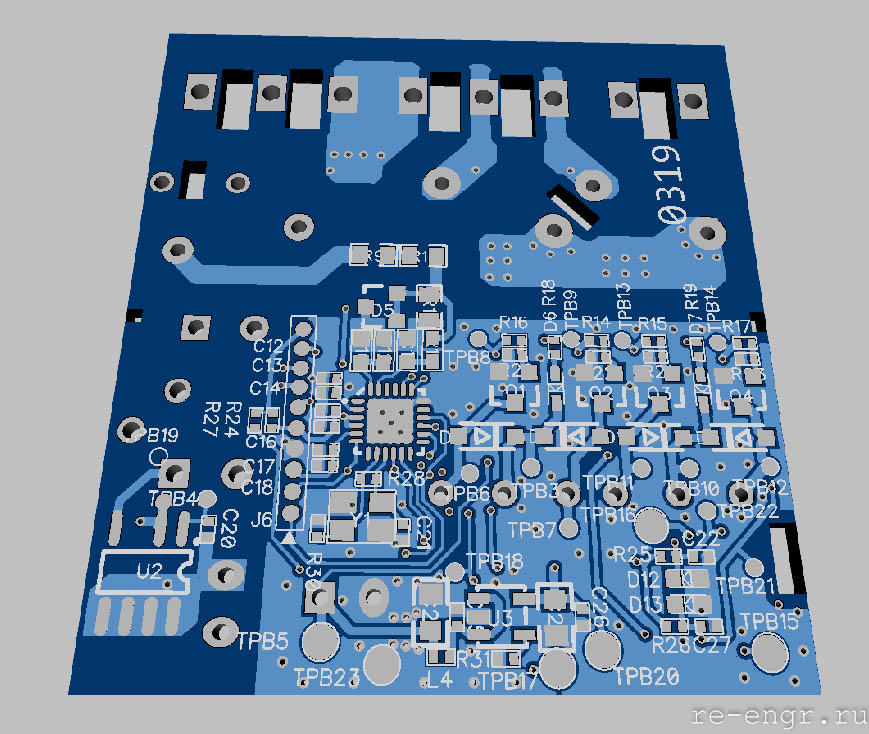

Стек слоёв

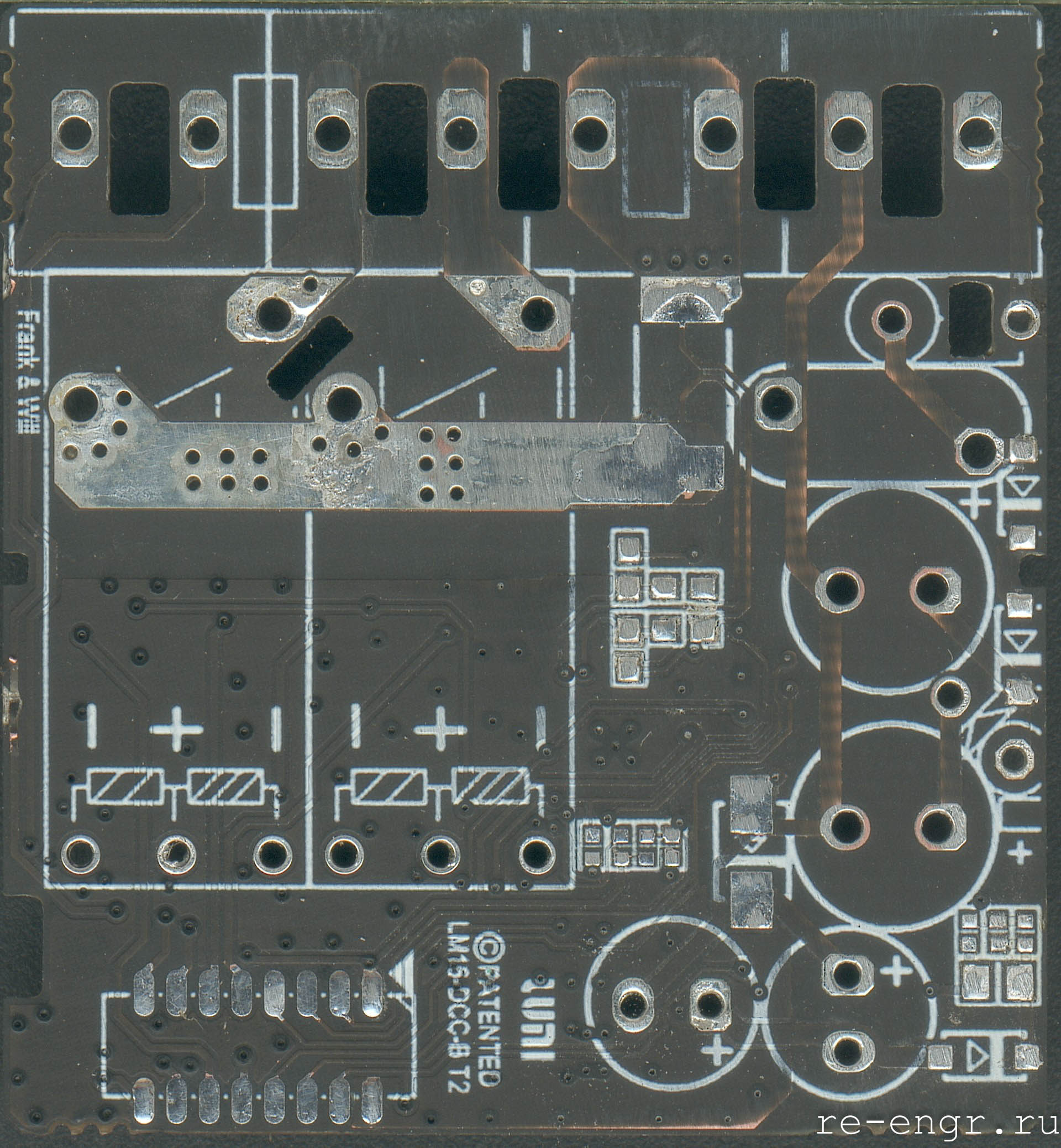

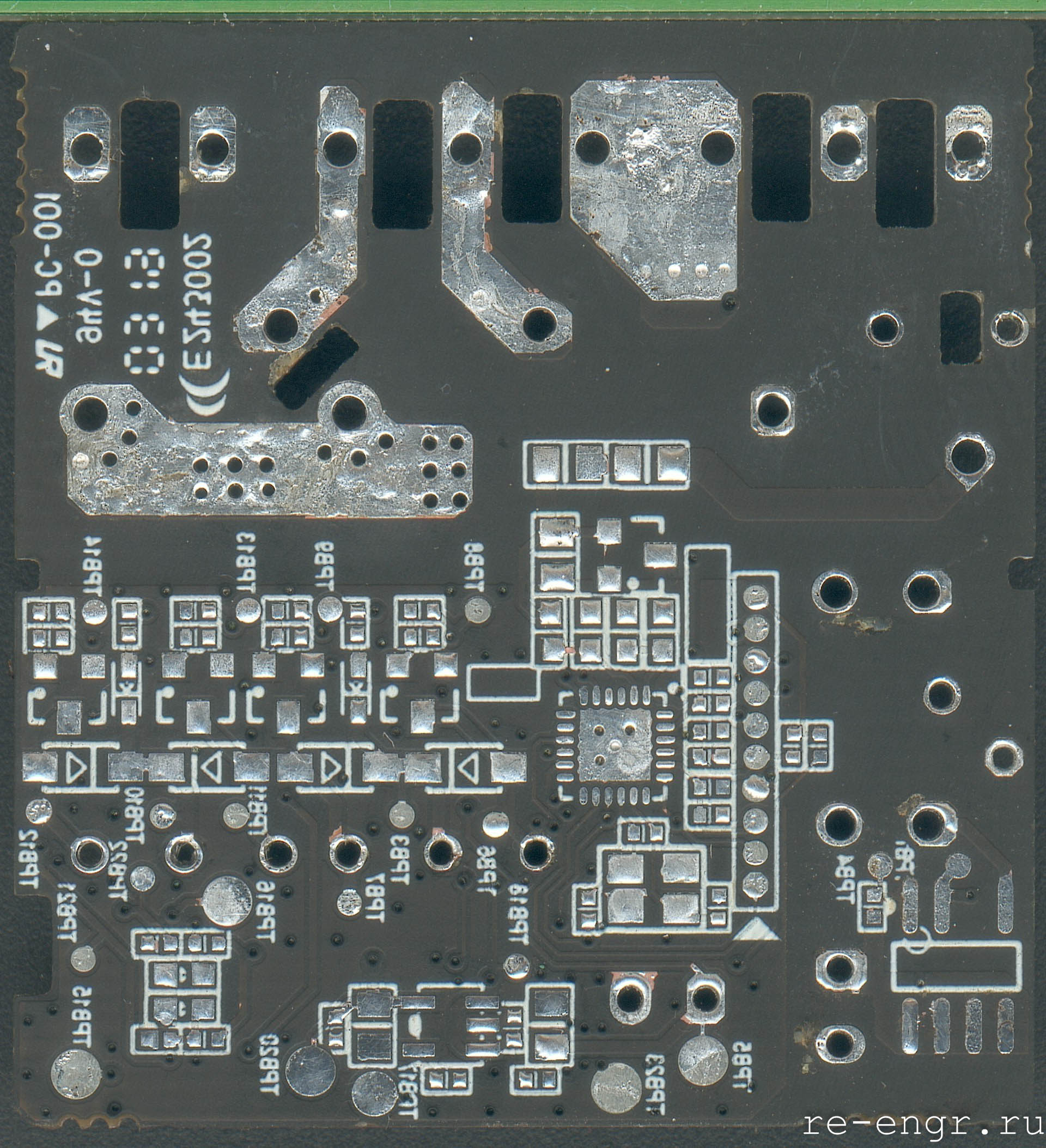

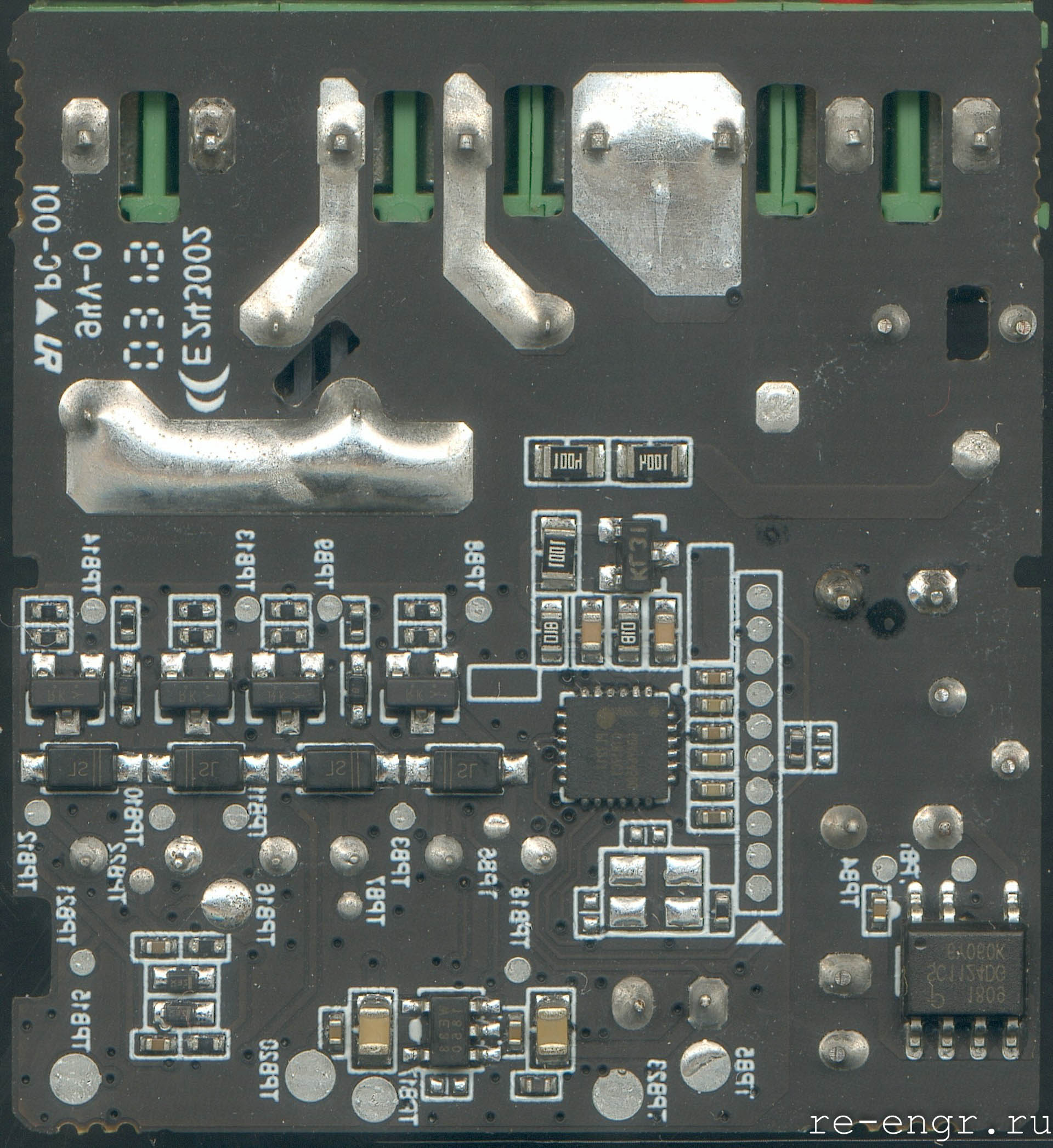

Плата двухслойная. Толщина платы 1.5 мм. Ниже представлены сканы каждого слоя расположенных ‘на просвет’ (слой bottom отзеркален).

Схема

В формате pdf

Схема.

Схема.

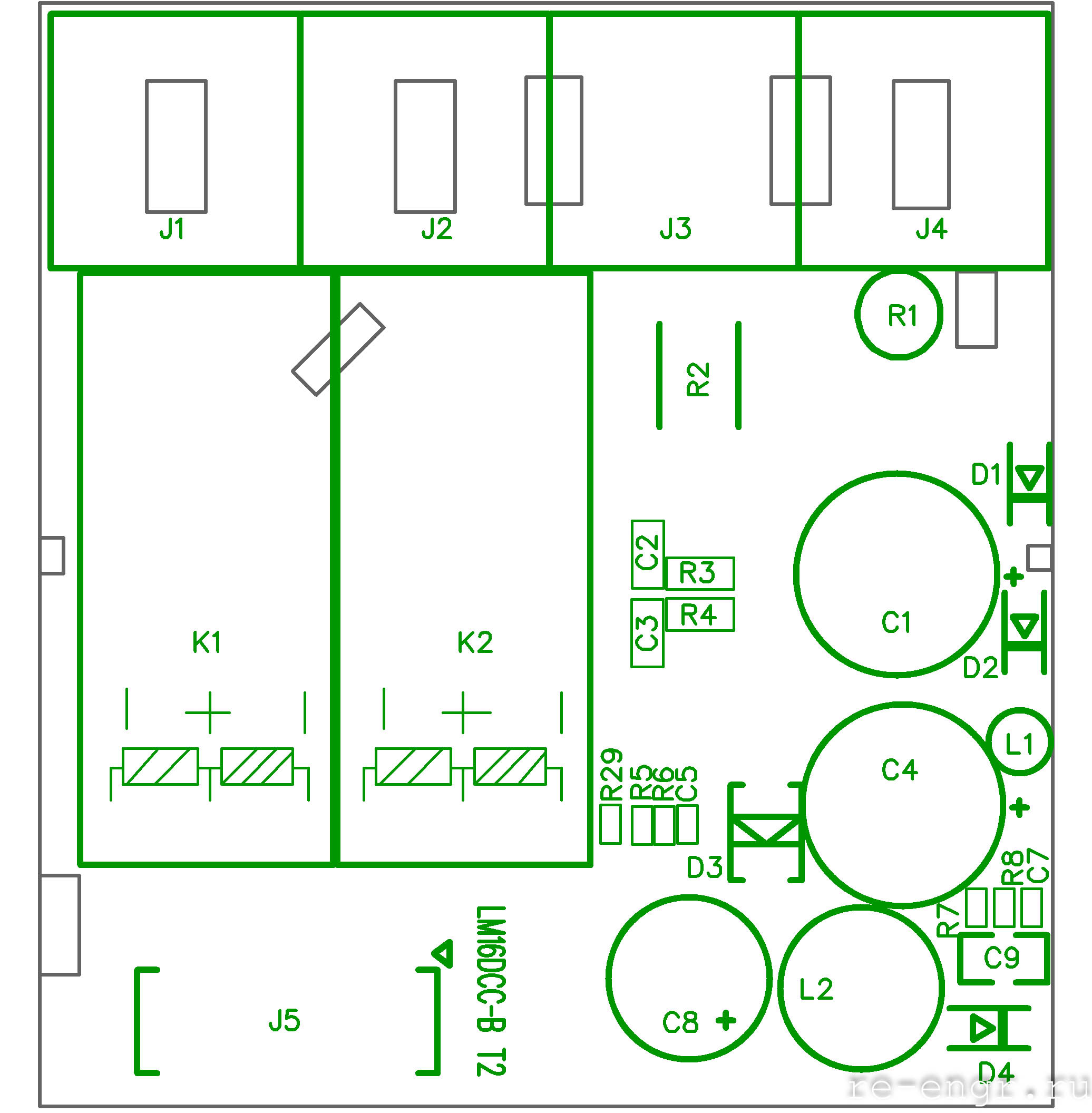

Сборочный чертеж. Сторона top.

Сборочный чертеж. Сторона top.

Сборочный чертеж. Сторона bottom.

Сборочный чертеж. Сторона bottom.

Остальная документация

Gerber файлы я пока не проверял в железе. DRC запускал с допусками JLCPCB.